Содержание

Как на самом деле делают процессоры? РАЗБОР / Хабр

Как создаются современные процессоры? Насколько это сложный и интересный процесс и почему так важна некая Экстремальная УФ-литография? В этот раз мы копнули действительно глубоко и готовы рассказать вам об этой магии технологий. Располагайтесь поудобнее, будет интересно.

Вот вам затравочка — 30-килоВаттный лазер в вакууме стреляет по капле олова и превращает ее в плазму — скажете фантастика?

А мы разберемся как это работает и расскажем об одной компании из Европы, которая стоит тенью за всеми гигантами Apple, AMD, Intel, Qualcomm, Samsung и другими и без нее никаких новых процессоров бы и не было. И нет это, к сожалению, не Чебоксарский завод электроники.

Чтобы понять процесс экстремальной ультрафиолетовой литографии — нам надо для начала понять, что вообще такое фотолитография. Сам процесс по своей сути очень похож на то как печатаются фотографии с пленочных негативов на фотобумагу! Не верите — сейчас все объясним.

Фотолитография

Начнем с простого примера — возьмем прозрачное стекло и нанесем на него какой-то геометрический рисунок, оставив при этом какие-то участки без краски. По сути, сделаем трафарет. Приложим этот кусок стекла к фонарику и включим его. Мы получим ровно тот же рисунок в виде тени, который мы нанесли на кусок стекла.

В производстве процессоров этот кусок стекла с рисунком называется маска. Маска позволяет получить на поверхности любого материала “засвеченные и незасвеченные” участки любой плоской формы.

Хорошо — рисунок на поверхности мы получили, но это всего лишь тень. Теперь надо как-то его там сохранить. Для этого на поверхность кремниевой пластины наносится специальный светочувствительный слой, который называют Фоторезистом. Для простоты мы не будем тут говорить о позитивных и негативных фоторезистах, почему они так реагируют, все-таки мы не на уроке Физической химии. Просто скажем, что это такое вещество, которое меняет свои свойства, когда на него попадает свет на определенной частоте, то есть на определенной длине волны.

Опять же как и на фотопленке или фотобумаге — специальные слои материалов реагируют на свет!

После того как нужные нам участки на кремнии мы засветили, именно их мы можем убрать, оставив при этом на месте остальные, то есть незасвеченные участки. В итоге мы получили тот рисунок, который и хотели. Это и есть фотолитография!

Конечно, кроме фотолитографии в производстве процессоров участвуют и другие процессы, такие как травление и осаждение, фактически комбинацией этих процессов вместе с фотолитографией транзисторы как-бы печатаются слой за слоем на кремнии.

Технология не новая, почти все процессоры начиная с 1960-х производятся при помощи фотолитографии. Именно эта технология открыла мир полевых транзисторов и путь ко всей современной микроэлектронике.

Но по-настоящему большой скачок в этой области произошел только недавно! С переходом на EUV. И всё из-за длины волны в 13.5 нм. Не переживайте, сейчас объясню!

Длина волны на которой светит наш “фонарик” — это невероятно важный параметр. Именно она и определяет насколько маленьким вы можете получить элементы на кристалле.

Именно она и определяет насколько маленьким вы можете получить элементы на кристалле.

Правило максимально простое: Меньше длина волны — больше разрешение, и меньше техпроцесс!

Обратите внимание на картинку. Абсолютно все процессоры начиная с начала 90-х до 2019 года производились с использованием процесса Глубокой УФ-литографии, или DUV литографии. Это то, что было до Экстремальной.

Он основывался на использовании фторид-аргонового лазера, который испускает свет с длиной волны в 193 нанометра. Этот свет лежит в области глубокого ультрафиолета — отсюда и название.

Он проходит через систему линз, маску и попадает на наш кристалл покрытый фоторезистом, создавая необходимый рисунок.

Но у этой технологии тоже были свои ограничения, завязанные на фундаментальных законах физики.

Какой же минимальный техпроцесс возможен? Смотрим на формулу (только не пугайтесь):

Здесь Лямбда — это и есть наша длина волны, а CD — это critical dimension, то есть минимальный размер получаемой структуры. То есть с использованием “старой” DUV литографии можно получить структуры не меньше примерно 50 нм. Но как же это так спросите вы? Ведь производители отлично делали и 14 и 10 нм, а кто-то даже и 7 нм с использованием DUV литографии.

То есть с использованием “старой” DUV литографии можно получить структуры не меньше примерно 50 нм. Но как же это так спросите вы? Ведь производители отлично делали и 14 и 10 нм, а кто-то даже и 7 нм с использованием DUV литографии.

Они пошли на хитрости. Вместо одного засвета через одну единую маску, они стали использовать несколько масок, с разными рисунками, которые дополняют друг-друга. Это процесс получил название множественное экспонирование. Назовем это принципом слоеного пирога!

Да — производители обошли прямые физические ограничения, но физику не обманули!

Появилась серьезная проблема: эти дополнительные шаги сделали производство каждого чипа гораздо дороже, из-за них увеличивается количества брака, есть и другие проблемы.

То есть в теории можно продолжить работать со старой технологией и путем игры с масками и экспонированием (двойная, тройная, четверная экспозиция) уменьшать размеры и дальше, но это сделает процы золотыми. Ведь с каждым слоем процент брака возрастает все выше, а ошибка накапливается!

То есть можно сказать, что DUV — это тупик! Что делать дальше, как уменьшать?

И тут на помощь приходит великая и ужасная технология Экстремальной УФ-литографии, или EUV-литографии!

Посмотрите на фото — оно прекрасно демонстрирует различие двух технологий. Обе получены с использованием 7-нанометрового техпроцесса, но та что слева получена с использованием DUV-литографии и с теми самыми хитростями о которых мы говорили — тройное экспонирование, то есть с поэтапным использованием 3 разных масок. Справа же — технология EUV литографии на 13.5 нанометрах, с использованием одной единственной маски — разница очевидна — границы гораздо четче, лучший контроль геометрии, ну и сам процесс намного быстрее, меньше процент брака, то есть в конце концов дешевле. Вот она дорога в светлое будущее, почему бы сразу так не делать, в чем проблема?

Обе получены с использованием 7-нанометрового техпроцесса, но та что слева получена с использованием DUV-литографии и с теми самыми хитростями о которых мы говорили — тройное экспонирование, то есть с поэтапным использованием 3 разных масок. Справа же — технология EUV литографии на 13.5 нанометрах, с использованием одной единственной маски — разница очевидна — границы гораздо четче, лучший контроль геометрии, ну и сам процесс намного быстрее, меньше процент брака, то есть в конце концов дешевле. Вот она дорога в светлое будущее, почему бы сразу так не делать, в чем проблема?

Как работает EUV-литография

Все дело в том, что хоть EUV это та же литография, внутри в деталях все гораздо сложнее и тут ученые и инженеры столкнулись с новыми проблемами!

Сама технология экстремальной УФ-литографии начала разрабатываться в самом начале 2000 годов. В ней используется источник, который излучает свет с длинной волны в 13.5 нанометров — то есть на нижней границе УФ-спектра, близко к рентгену!

В теории этим способом можно создавать структуры уже критических размеров — настолько маленьких, что еще чуть-чуть и на них перестанут действовать законы обычной физики. То есть после 5 нм мы попадаем в квантовый мир!

То есть после 5 нм мы попадаем в квантовый мир!

Но даже эта проблема на данный момент решена. Есть источник — возьми, да и делай себе сколь угодно маленькие процессоры.

Все совсем не так просто!

Проблема таких коротких длин волн в том, что они поглощаются почти всеми материалами, поэтому обычные линзы что были раньше уже не подходят. Что делать?

Для управления таким светом было принято решение создать специальные отражающие зеркальные линзы. И эти линзы должны быть гладкими! Очень гладкими!!! Практически идеально гладкими!

Вот вам аналогия — растянем линзу до размеров, скажем, Германии, так вот ее поверхность должна быть такой гладкой, что ничего не должно выпирать больше чем на 1 миллиметр. Этот параметр называется шероховатостью линзы и у нужной нам он должен быть меньше 0.5 нанометра. Это уже близко к размерам АТОМА! Кто же сможет подковать блоху?

Конечно, Zeiss — только они на это способны! Да — та самая компания Zeiss, чьи линзы стоят на моем фотике, были в Nokia или во флагманах Sony Xperia.

Одна проблема решена — линзы есть!

Есть и вторая — этот свет рассеивается даже в простом воздухе. Поэтому для того чтобы процесс прошел нормально его надо проводить в вакууме!

Про частички пыли и грязи я вообще молчу — понятно что их там вообще не должно быть. Чистые комнаты на таком производстве на порядки чище, чем операционные в больницах! Люди буквально ходят в скафандрах. Любая, даже самая маленькая частичка грязи, кожи или воздуха может испортить и маску и зеркала!

А что же с источником? Просто поставили специальный лазер на более короткую длину волны и все? Проблема в том, что ни лампочек, ни лазеров, ни каких-либо других нормальных источников света, которые излучают на такой длине волны просто не существует в природе.

И как же тогда получают нужное излучение? Элементарно, Ватсон — нам нужна плазма.

Надо нагреть оловянный пар до температур в 100 раз больших, чем температура поверхности солнца! Всего-то! И за этим стоит почти 2 десятилетия разработок.

В установке для производства процессоров по EUV-литографии, о которой мы поговорим отдельно установлен специальный углекислотный лазер, который опять же может производиться в тандеме всего двух компаний в мире — немецкой фирмой Trumpf и американской Cymer. Этот монстр мощностью в 30 киловатт стреляет по 2 импульса с частотой 50 килогерц.

Лазер попадает в капли олова, первый выстрел фактически плющит и превращает каплю в блин, которая становится легкой мишенью для второго залпа, который ее поджигает. И происходит это 50 тысяч раз в секунду! А образовавшаяся плазма и излучает этот свет в экстремальном УФ спектре.

И естественно, это только самая база, но мы попробовали нарисовать вам картину того насколько это сложный и крутой процесс.

Компания, стоящая за производством всех процессоров

О технологии рассказали, значит ее кто-то придумал и реализовал, но ее разработка оказалась настолько дорогой, что даже крупные гиганты и воротилы не способны потянуть такие бюджеты!

В итоге, чтобы это стало реальностью всем пришлось скинуться — Intel в 2012 году, а TSMC и Samsung где-то в 2015 году приняли участие в общем проекте. Суммарные инвестиции составили, по разным оценкам от 14 до 21 млрд долларов! Из которых почти 10 млрд были вложены в одну единственную нидерландскую компанию ASML. Именно она и стоит за всем производством процессоров в мире по методу EUV-литографии! Вау! Что за ASML и почему мы о ней ничего не слышали? Компания из Нидерландов — что за темная лошадка?

Суммарные инвестиции составили, по разным оценкам от 14 до 21 млрд долларов! Из которых почти 10 млрд были вложены в одну единственную нидерландскую компанию ASML. Именно она и стоит за всем производством процессоров в мире по методу EUV-литографии! Вау! Что за ASML и почему мы о ней ничего не слышали? Компания из Нидерландов — что за темная лошадка?

Все дело в том, что ASML создали тот самый инструмент без которого Apple, Самсунг и Intel с AMD фактически как без рук! Речь идет об установке стоимостью более 120 миллионов долларов. Она огромная, 180-тонная, потребляет почти 1 мегаватт электроэнергии, и ей нужно почти 1.5 тонны воды в минуту для охлаждения! Но даже при такой цене очереди на них стоят годами ведь в год этих машин производится несколько десятков штук.

Тут же стоит упомянуть немалый вклад российских умов. Например, один из создателей этой технологии — Банин Вадим Евгеньевич, сейчас директор по разработке в ASML. Также в компании работают и другие наши соотечественники!

Мы выяснили, что эта компания делает одни из самых технологичных девайсов, в котором собраны все знания человечества и на них производят процессоры все IT-гиганты сразу!

Но не только ASML стоит за спиной нам известных IT-гигантов. Их установки состоят из более чем 100 тысяч деталей, которые производятся более чем тысячью компаний по всему миру. Все эти компании связаны друг с другом!

Их установки состоят из более чем 100 тысяч деталей, которые производятся более чем тысячью компаний по всему миру. Все эти компании связаны друг с другом!

Будущее

Но что же будет дальше! Вы что — думали, что мы оставим вас оставим в дне сегодняшнем? Нет — мы подглядели в будущее! Мы раздобыли информацию что будет после пяти или даже двух нм!

Во-первых, прямо сейчас, пока вы смотрите это видео, TSMC уже штампует новые процессоры для HUAWEI, Apple и Samsung с использованием EUV-литографии, но не на 7 нм, как было с Apple A13 и Kirin 990, а на 5 нм техпроцессе! И этому есть множества подтверждений! И о них мы услышим уже этой осенью. Как вам такое — A14 Bionic будет 5нм! Так же ждем новые Exynos на 5 нм и процессоры Google, о которых мы рассказывали отдельно! Qualcomm наверняка тоже подтянется за ними, но тут мы не располагаем данными!

А во-вторых, и это вообще взрывает мозг, ASML уже заканчивает разработку установок, которые позволят производить процессоры на 2 нанометровом техпроцессе и даже меньше всего через 4-5 лет!

Для этого ребята из нидерландской компании совместно с немецкой Zeiss разработали новые зеркальные линзы, с высокими значениями апертуры. Это анаморфная оптика — она и многое другое позволит увеличить разрешающую способность.

Это анаморфная оптика — она и многое другое позволит увеличить разрешающую способность.

Сам процесс по сути тот же EUV, но с приставкой High-NA EUV. А сами агрегаты будут занимать еще больше места, посмотрите вот так для них делают оптику!

Этот год тяжелый для всех, но в тоже время — посмотрите какими шагами начинают развиваться технологии, все шире и шире. Нас ждут новые процессоры с мощностями, которые нам и не снились.

Кроме этого развиваются совершенно новые типы процессоров такие как NPU — для нейровычислений.

Как делают процессор или ЦП: литография и упаковка

10 мая 2021

Мэтт Миллс

аппаратные средства

0

В современную эпоху мы не можем представить себе вычисления без процессор , Которая также называется ЦП (Центральный процессор на английском языке). Мы используем их в компьютерах, смартфонах и даже на телевидении, но задумывались ли вы когда-нибудь? как сделан процессор ? В этой статье мы расскажем вам об этом очень подробно, чтобы вы могли понять, на что похож этот процесс, от его концепции до готового продукта, который мы все используем.

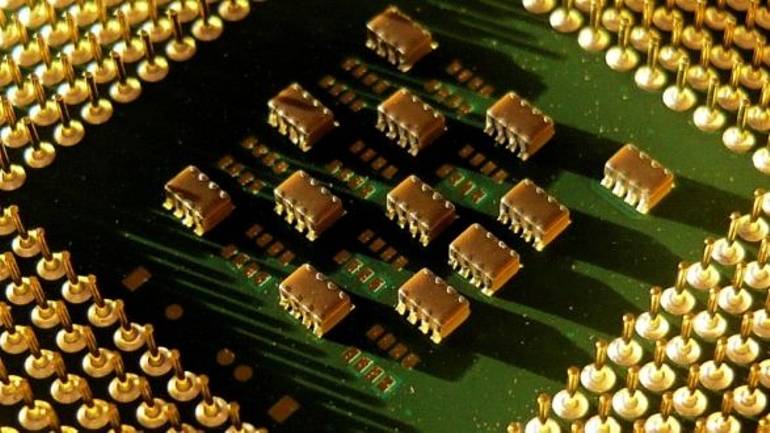

Большинство пользователей понимают, что процессор представляет собой простое оборудование, которое устанавливается на материнская плата и это выделяет много тепла. Однако процессор состоит из тысяч сложных элементов, что позволяет ему выполнять математические операции, необходимые для того, чтобы все работало, поскольку в конечном итоге все, что делает компьютер, обязательно должно проходить через процессор, включая что это обрабатывается GPU / ГРАФИЧЕСКИЙ ПРОЦЕССОР, поэтому это так важно.

Содержание

- Как сделан ЦП

- Фотолитография — это то, что оживляет процессоры

- Проблемы наноразмерной фотолитографии

- Упаковка, необходимая в процессе производства ЦП

Хотя принцип работы процессоров может показаться волшебным, это результат десятилетий умной инженерии. Поскольку транзисторы, элементы, из которых состоит большинство процессоров, уменьшены до микроскопических размеров, способ изготовления процессоров становится все более сложным.

Фотолитография — это то, что оживляет процессоры

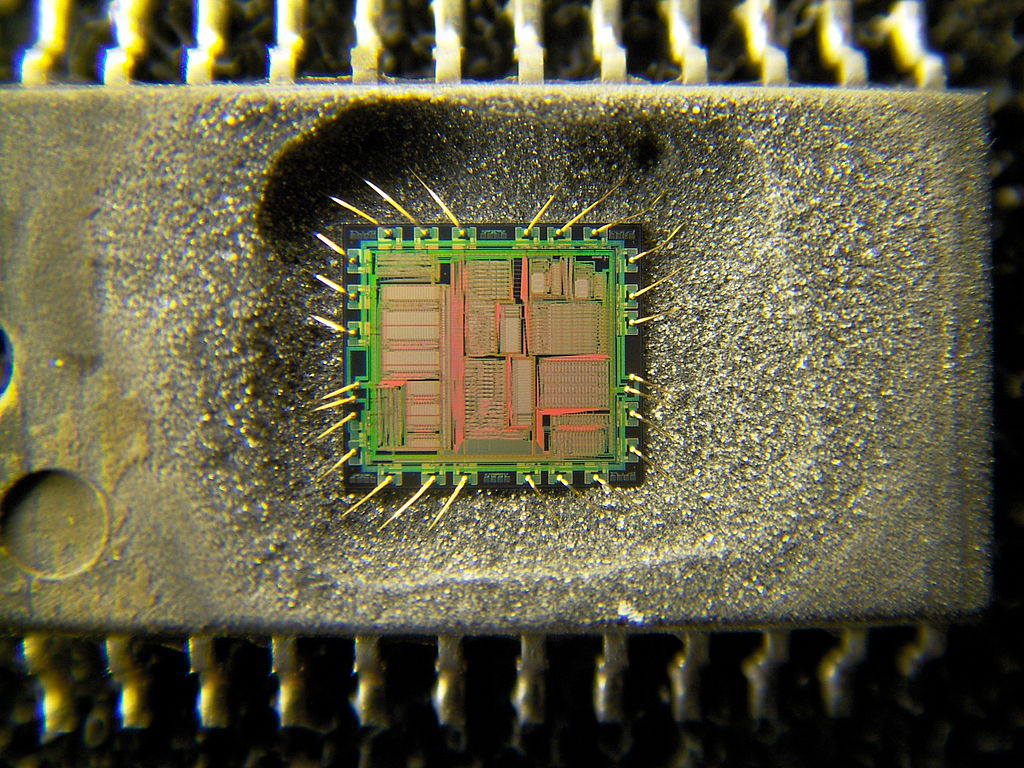

Мы привыкли видеть пластины, заполненные десятками микросхем, которые затем используются в процессорах, но чтобы добраться туда, вам нужно пройти ряд шагов, которые начинаются с фотолитография .

Транзисторы сейчас настолько малы, что производители не могут построить их обычными методами. Хотя прецизионные токарные станки и даже 3D-принтеры могут создавать невероятно сложные творения, они обычно достигают уровня микрометрической точности (это примерно тридцать тысячных дюйма), но они по-прежнему не подходят для нано-масштабов, в которых они созданы. фишки сегодня.

Фотолитография решает эту проблему, избавляя от необходимости перемещать сложное оборудование с большой точностью. Вместо этого он использует свет для гравировки изображения на кремниевом чипе, как если бы это был старый проектор, который можно было найти в школьных классах, но наоборот, уменьшая масштаб шаблона до желаемой точности.

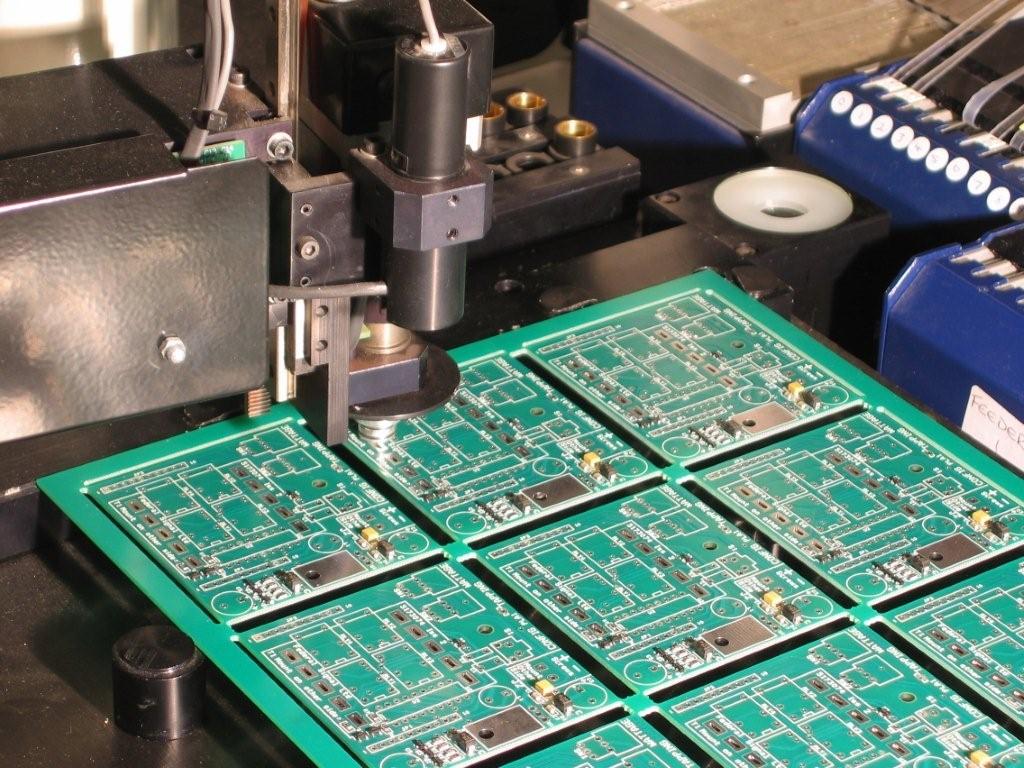

Таким образом, изображение проецируется на кремниевую пластину, которая обрабатывается с чрезвычайно высокой точностью на специальных станках (знаменитые станки производства ASML) и в чрезвычайно жестких условиях, поскольку любая пылинка на пластине может означать, что она будет полностью испорчена. . Пластина покрыта материалом, называемым фоторезистом, который реагирует на свет и реагирует на него, оставляя травление на ЦП, которое может быть заполнено медью или другими материалами для формирования транзисторов. Затем этот процесс повторяется много раз, увеличивая размер процессора, так же, как 3D-принтер накапливает слои пластика.

Проблемы наноразмерной фотолитографии

Неважно, можете ли вы делать транзисторы все меньше и меньше, если транзисторы не могут работать, а у наноразмерной технологии есть много проблем с физикой из-за размера. Транзисторы должны останавливать поток электричества, когда они выключены, но они становятся настолько маленькими, что электроны иногда могут проходить через них. Это называется квантовым туннелированием, и это огромная проблема для инженеров по кремнию.

Это называется квантовым туннелированием, и это огромная проблема для инженеров по кремнию.

Еще одна проблема — дефекты; Даже у фотолитографии есть предел точности, она в некотором роде аналогична размытому изображению от проектора, который не показывает такое четкое изображение при его увеличении или уменьшении. Кремниевые фабрики в настоящее время пытаются смягчить этот эффект, используя технологию EUV (экстремальное ультрафиолетовое излучение), длину волны намного превышающую человеческую, используя лазеры в вакуумной камере. Однако эта проблема будет сохраняться, поскольку размер продолжает уменьшаться.

Иногда дефекты можно уменьшить с помощью процесса, называемого биннингом: если дефект затрагивает ядро ЦП, это ядро отключается, и чип продается как младшая часть. Фактически, большинство линеек ЦП сделаны с использованием одной и той же модели, но у них отключены ядра, потому что они вышли из строя и поэтому продаются по более низкой цене как недорогой продукт.

Если дефект касается, например, кеш-памяти или другого важного компонента, микросхему, вероятно, придется утилизировать, что приведет к снижению производительности производства и, следовательно, к более высоким ценам. Текущие технологические узлы, такие как 7 и даже 10 нм, имеют более высокую пропускную способность, чем узлы 5 нм, и поэтому верно обратное, их цена ниже.

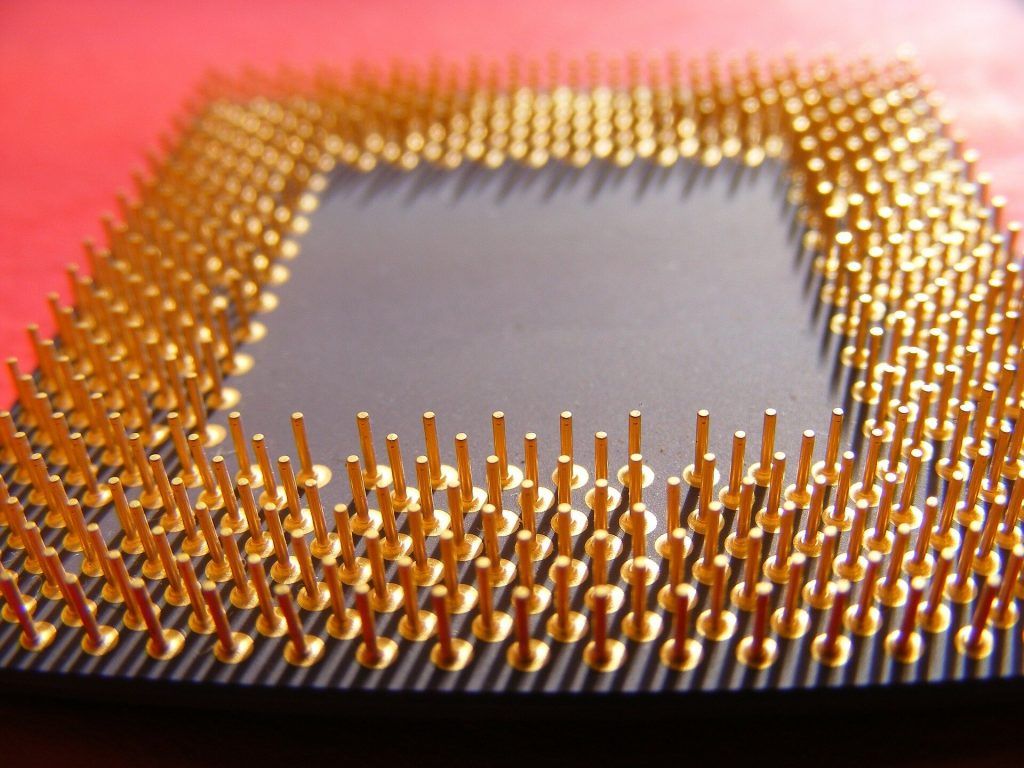

Упаковка, необходимая в процессе производства ЦП

Следуя процессу производства ЦП, как только у нас будут готовы микросхемы, их нужно упаковать для использования потребителями, и это гораздо больше, чем просто положить их в коробку с пенопластом. Когда ЦП готов, он по-прежнему бесполезен, если его нельзя подключить к остальной части системы, поэтому процесс «упаковки» или «упаковки» относится к методу, при котором тонкая силиконовая матрица (кристалл) прикрепляется к PCB, которую большинство людей считают процессором.

Этот процесс требует большой точности, но, очевидно, не такой большой, как предыдущие шаги. Матрица ЦП установлена на силиконовой плате, и электрические соединения проходят на всех контактах, которые контактируют с разъемом материнской платы. Современные процессоры могут иметь тысячи контактов, например AMD Процессоры Threadripper, у которых их 4096 штук.

Матрица ЦП установлена на силиконовой плате, и электрические соединения проходят на всех контактах, которые контактируют с разъемом материнской платы. Современные процессоры могут иметь тысячи контактов, например AMD Процессоры Threadripper, у которых их 4096 штук.

Поскольку ЦП выделяет много тепла и должен также защищать свою целостность с другой стороны, наверху устанавливается встроенный теплоотвод или английский IHS. Это соприкасается с матрицей и отводит тепло от матрицы, которое затем охлаждается с помощью кулера процессора. Для некоторых энтузиастов термопаста, используемая для этого соединения, недостаточно хороша, поэтому некоторые решают выполнить процесс удаления с процессором.

После того, как все собрано, его можно упаковать в настоящие коробки, готовые к отправке на полки магазинов и установке на наши компьютеры. Теперь, когда вы знаете, как делается ЦП и насколько сложно его сделать, удивительно, что большинство современных ЦП стоят всего несколько сотен долларов, верно?

- процессор

Процесс литографии

7 нм — WikiChip

|

V · D · E

. Массовое производство интегральных схем, изготовленных с использованием 7-нм техпроцесса, началось в 2018 году. К 2020/21 году передовые литейные производства будут поэтапно отказываться от этого техпроцесса, где он будет заменен 5-нм узлом.

Массовое производство интегральных схем, изготовленных с использованием 7-нм техпроцесса, началось в 2018 году. К 2020/21 году передовые литейные производства будут поэтапно отказываться от этого техпроцесса, где он будет заменен 5-нм узлом.

Термин «7 нм» — это просто коммерческое название поколения определенного размера и его технологии, и не представляет собой какую-либо геометрию транзистора.

Содержание

- 1 Обзор

- 1.1 Плотность

- 2 Промышленность

- 2.1 Интел

- 2.1.1 Интел 7

- 2.1.1.1 Intel 7 Ультра

- 2.1.1 Интел 7

- 2.2 ТСМС

- 2.2.1 N7

- 2.2.1.1 Стандартные ячейки

- 2.2.2 N7P

- 2.2.3 N7+

- 2.2.1 N7

- 2.3 Самсунг

- 2.3.1 7LPE

- 2.3.2 7ЛПП

- 2.4 GlobalFoundries

- 2.4.1 7LP

- 2.4.2 7HPC

- 2.1 Интел

- 3 микропроцессора 7 нм

- 4 микроархитектуры 7 нм

- 5 См.

также

также - 6 Библиография

Обзор[править]

Впервые представлен крупными литейными заводами в 2018-19 гг.Во временном интервале 7-нанометровый технологический процесс характеризуется использованием транзисторов FinFET с шагом ребер в 30 нанометров и самым плотным металлическим шагом в верхних 30 или 50 нанометров. Из-за небольших размеров элементов для некоторых слоев пришлось использовать четырехъядерный паттерн. Этот процесс был введен как раз тогда, когда литография EUV была готова к массовому производству, поэтому некоторые литейные заводы использовали EUV, а другие нет.

Плотность[править]

С точки зрения исходной плотности на уровне ячеек, 7-нанометровый узел имеет плотность кремния между 90–102 миллиона транзисторов на квадратный миллиметр, согласно собственному анализу WikiChip.

Промышленность[править]

Только три компании в настоящее время планируют или разрабатывают 7-нанометровый узел: Intel, TSMC и Samsung.

| Intel | TSMC | Samsung | GlobalFoundries | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Process | P1276 (CPU), P1277 (SoC) | N7, N7P, N7+ | 7LPE, 7LPP | | ||||||||

| Production | 2021 | April 2018 | April 2019 | Cancelled | ||||||||

| Litho | Lithography | EUV | DUV ⇒ EUV | EUV | DUV ⇒ EUV | |||||||

| Immersion Экспозиция | SADP ⇒ SE (EUV) DP (193i) | SE (EUV) DP (193i) | SE (EUV) DP (193i) | SE (EUV) D0006 | SADP ⇒ SE (EUV) DP (193i) | |||||||

| Wafer | Type | Bulk | ||||||||||

| Size | 300 mm | |||||||||||

| xTor | Type | FinFET | ||||||||||

| Voltage | ||||||||||||

| Value | 10 nm Δ | Value | 10 nm Δ | Value | 10 nm Δ | Value | 14 nm Δ | |||||

| Fin | Pitch | 30 nm | 0. 83x 83x | 27 nm | 0.64x | 30 nm | 0.625x | |||||

| Width | 6 nm | 1.00x | ||||||||||

| Height | 52 nm | 1.24x | ||||||||||

| Gate Length (L g ) | 8/10 nm | |||||||||||

| Contacted Gate Pitch (CPP) | 64 nm (HP) 57 nm (HD) | 0.82x | 60 nm (HP) 54 nm (HD) | 0.79x | 56 nm | 0.72x | ||||||

| Minimum Metal Pitch (MMP) | 40 nm | 0.95x | 36 nm | 0.75x | 40 nm | 0,625x | ||||||

| Статическое ОЗУ | High-Perf (HP) | 0.032 µm² | 0. 65x 65x | 0.0353 µm² | 0.44x | |||||||

| High-Density (HD) | 0.027 µm² | 0.64x | 0.026 µm² | 0.65x | 0.0269 µm² | 0.42x | ||||||

| Low-Voltage (LV) | ||||||||||||

Intel[edit]

Intel 7[edit]

Intel 7 Ultra[править]

Новая кривая V-F для усовершенствованного процесса Intel 7.

Intel представила расширенную версию процесса Intel 7 в конце 2022 года с выпуском процессоров Core 13-го поколения на базе микроархитектуры Raptor Lake. Новый процесс, получивший внутреннее прозвище «Intel 7 Ultra» , представляет собой полное обновление PDK по сравнению с тем, который используется Alder Lake, их архитектурой SuperFin Transistor 3-го поколения. Intel заявляет, что этот процесс позволяет получить транзисторы со значительно лучшей мобильностью каналов. Компания заявляет, что на самом верхнем конце кривой V-F пиковая частота теперь почти на 1 ГГц выше. Сама кривая была улучшена, сдвинув частоты предыдущего поколения примерно на 200 МГц при напряжении ISO или, альтернативно, снизив напряжение более чем на 50 мВ при частоте ISO.

Компания заявляет, что на самом верхнем конце кривой V-F пиковая частота теперь почти на 1 ГГц выше. Сама кривая была улучшена, сдвинув частоты предыдущего поколения примерно на 200 МГц при напряжении ISO или, альтернативно, снизив напряжение более чем на 50 мВ при частоте ISO.

TSMC[править]

TSMC начала массовое производство своего 7-нанометрового узла N7 в апреле 2018 года. Хотя TSMC выпустила 10-нанометровый узел годом ранее, компания считала его 10-нм узлом недолговечным и предназначалась для обучения узлу на пути к 7. В начале 2019 года TSMC представила вторую версию технологического процесса. его процесс N7 называется N7P , что обеспечивает дополнительные улучшения производительности. С появлением высокопроизводительных машин EUV, готовых к массовому производству, TSMC представила третий вариант под названием 9.0122 N7+ , использующий EUV.

N7[править]

Обзор N7

Оригинальный TSMC 7-нанометровый процесс N7 был представлен в апреле 2018 года. По сравнению с собственной 16-нанометровой технологией, TSMC утверждает, что ее 7-нанометровый узел обеспечивает повышение скорости примерно на 35-40%. или на 65% ниже мощность. Говорят, что по сравнению с 10-нм узлом с половинным узлом N7 обеспечивает повышение скорости на ~ 20% или снижение энергопотребления на ~ 40%. Говорят, что с точки зрения плотности N7 обеспечивает улучшение в 1,6 и 3,3 раза по сравнению с N10 и N16 соответственно. N7 в значительной степени основан на всех предыдущих процессах FinFET, которые компания использовала ранее. С этой целью это FinFET четвертого поколения, HKMG пятого поколения, последний затвор, оксидный процесс с двумя затворами.

По сравнению с собственной 16-нанометровой технологией, TSMC утверждает, что ее 7-нанометровый узел обеспечивает повышение скорости примерно на 35-40%. или на 65% ниже мощность. Говорят, что по сравнению с 10-нм узлом с половинным узлом N7 обеспечивает повышение скорости на ~ 20% или снижение энергопотребления на ~ 40%. Говорят, что с точки зрения плотности N7 обеспечивает улучшение в 1,6 и 3,3 раза по сравнению с N10 и N16 соответственно. N7 в значительной степени основан на всех предыдущих процессах FinFET, которые компания использовала ранее. С этой целью это FinFET четвертого поколения, HKMG пятого поколения, последний затвор, оксидный процесс с двумя затворами.

| N7 PPA против N16 | ||

|---|---|---|

| Скорость при изо-мощности | Мощность при скорости ISO | Плотность |

| ~30% | ~55% | ~3,3x |

| N7 PPA против N10 | ||

| Скорость при изо-мощности | Мощность при скорости ISO | Плотность |

| ~20% | ~40% | ~1,6x |

Вт эфф для TSMC 16, 10 и 7 нм.

Для N7 TSMC продолжала использовать иммерсионную литографию ArF с длиной волны 193 нм в глубоком ультрафиолете (DUV). Ограничения i193 диктовали некоторые правила проектирования процесса. Для транзистора шаг затвора был дополнительно уменьшен до 57 нм, однако шаг межсоединений был остановлен на отметке 40 нм, чтобы сохранить структуру в точке SADP. Правила проектирования были тщательно разработаны, чтобы оставаться в рамках двойного шаблона. Единичный паттерн был немного продвинут до точки 76 нанометров. Правила проектирования для N7 показаны ниже.

| Правила проектирования TSMC N7 | |||

|---|---|---|---|

| Слой | Шаг (нм) | Моделирование | Примечания |

| Плавник | 30 | СКП | |

| Поли | 57 | САДП | |

| М0 | 40 | САДП | Мкс |

| М1 | 40 | САДП | 1x |

| М2 | 40 | САДП | 1x |

| М3 | 40 | САДП | 1x |

| М4 | 40 | САДП | 1x |

| М5 | 76 | Одноместный | 1,9x |

| М6 | 76 | Одноместный | 1,9x |

| М7 | 76 | Одноместный | 1,9x |

| М8 | 76 | Одноместный | 1,9x |

| М9 | 76 | Одноместный | 1,9x |

| М10 | 124 | Одноместный | 3,1x |

| М11, М12 | 720 | Одноместный | 18x |

Стоит отметить, что агрессивное масштабирование шага ребер привело к довольно плотным битовым ячейкам SRAM. Размер битовой ячейки SRAM высокой плотности N7 составляет 0,027 мкм².

Размер битовой ячейки SRAM высокой плотности N7 составляет 0,027 мкм².

Распространение элементов SoC Apple A12 (MSS Corp). Видны кобальтовые контакты.

Профиль транзистора также был улучшен. Как и в 10-нанометровом техпроцессе Intel, TSMC представила кобальтовое наполнение траншейных контактов, заменив вольфрамовые контакты. Это приводит к снижению сопротивления в этой области на 50%. Некоторые преимущества масштабирования площади и затрат были достигнуты за счет масштабирования шага / высоты ребра. Продолжая масштабировать ширину ребра, вы получаете более узкий канал, в то время как увеличение высоты для поддержания хорошей эффективной ширины делается для того, чтобы улучшить характеристики короткого канала и подпороговый наклон (т. е. улучшить Ieff / Ceff), но это также ухудшает общие паразитные характеристики. Имейте в виду, что в целом задержка устройства CV/I все же лучше, потому что собственная емкость, такая как Cgate и Cov, по-прежнему зависит от Ieff.

Еще один способ визуализировать эффект масштабирования ширины и высоты — использовать эффективную ширину. На графике, показанном слева, мы нанесли эффективную ширину от 16 нанометров TSMC до текущего 7-нанометрового узла. По сравнению с N16, N7 имеет более чем в два раза большую эффективную ширину канала.

Для этого процесса были разработаны различные многовольтные устройства с диапазоном Vt около 200 мВ.

Стандартные ячейки Эти клетки имеют высоту 240 нм и 300 нм соответственно. До выхода на полную производственную мощность у TSMC изначально было 9Вариант T HP, который опирался на 57-нм CPP. Эта библиотека в конечном итоге устарела в пользу 64-нм библиотеки CPP 7.5T, которая сейчас используется в массовом производстве различными компаниями. Обратите внимание, что модели 7,5T и 9T схожи по мощности и производительности. Некоторые ранние проекты, которые начинались с библиотеки 9T, продолжали использовать ее, несмотря ни на что.

| Тип | Высокая плотность | Высокая производительность | |

|---|---|---|---|

| Название | h340 HD | h400 HP | H460 HP |

| FIN PINKE | 30 нм | ||

| Металл | 40 нм (наименьшая высота, используемая с DP) 76 нм (самый маленький шаг с SP) | 9 76 нм (самый маленький шах | 64 нм | 57 нм |

| Высота | 240 нм 8-фин X 30 нм | 300 нм 10-финал X 30 нм | 360 нм 12-FIN x 30 NM | 360 Нм 12-FIN X 30 NM | 99999. 360 Нм 360 Нм 12-FIN x 30 0009 | 360 нм 12-фина | 6 Т | 7,5 т | 9 т |

Qualcomm Snapdragon 855Ieff разница между ячейками HD и HP. (VLSI 2019)

Компания Qualcomm сообщила, что на ее собственной SoC (Snapdragon 855) высокопроизводительные элементы обеспечивают примерно на 10-13% более высокий эффективный управляющий ток (Ieff), хотя и за счет того, что транзисторы немного менее герметичны. Основываясь на собственном анализе WikiChip, плотные ячейки имеют около 91,2 МТр/мм², в то время как менее плотные высокопроизводительные ячейки рассчитываются примерно на уровне 65 МТр/мм².

N7P[править]

Улучшения N7P (2-го поколения) по сравнению с N7 (1-го поколения). (VLSI 2019)

В 2019 году TSMC представила процесс N7 2-го поколения под названием N7 Performance-Enhanced ( N7P ). N7P — это оптимизированная версия процесса TSMC N7. с этой целью он остается процессом, основанным на DUV, с соблюдением тех же правил проектирования и полностью IP-совместим с N7. N7P вводит оптимизации FEOL и MOL, которые, как говорят, приводят либо к повышению производительности на 7% при мощности изо, либо к снижению энергопотребления до 10% при скорости изо.

с этой целью он остается процессом, основанным на DUV, с соблюдением тех же правил проектирования и полностью IP-совместим с N7. N7P вводит оптимизации FEOL и MOL, которые, как говорят, приводят либо к повышению производительности на 7% при мощности изо, либо к снижению энергопотребления до 10% при скорости изо.

| N7 PPA против N7P | ||

|---|---|---|

| Скорость при изо-мощности | Мощность @ ISO-скорость | |

| ~7% | ~10% | |

Для своего процесса второго поколения TSMC внесла некоторые дополнительные оптимизации, включая оптимизацию профиля ребер, эпиоптимизацию, оптимизацию сопротивления MOL, уменьшение емкости FEOL и оптимизацию металлических затворов. Кроме того, при той же утечке на высоких частотах 7-нм техпроцесс второго поколения улучшил Vmin на 50 мВ.

N7+[править]

Узел N7+ — первая технология TSMC, использующая литографию EUV. Он не связан ни с процессами N7, ни с N7P и не совместим с IP ни с одним из них, что требует повторной реализации (новой физической схемы и проверки). N7+ поступил в массовое производство во втором квартале 2019 года и использует EUV для четырех критических слоев. Говорят, что по сравнению с процессом TSMC N7, N7+ обеспечивает повышение плотности примерно в 1,2 раза. Также сообщается, что N7+ обеспечивает на 10% более высокую производительность при изо-мощности или, в качестве альтернативы, до 15% более низкое энергопотребление при изо-производительности. На бумаге N7+ кажется немного лучше, чем N7P, хотя это достигается за счет повторной реализации дизайна.

N7+ поступил в массовое производство во втором квартале 2019 года и использует EUV для четырех критических слоев. Говорят, что по сравнению с процессом TSMC N7, N7+ обеспечивает повышение плотности примерно в 1,2 раза. Также сообщается, что N7+ обеспечивает на 10% более высокую производительность при изо-мощности или, в качестве альтернативы, до 15% более низкое энергопотребление при изо-производительности. На бумаге N7+ кажется немного лучше, чем N7P, хотя это достигается за счет повторной реализации дизайна.

| N7 PPA против N7+ | ||

|---|---|---|

| Скорость при изо-мощности | Мощность при скорости ISO | Плотность |

| ~10% | ~15% | 1,2x |

Samsung[править]

Samsung будет использовать EUVL для своего 7-нм узла и, таким образом, станет первой, кто представит эту новую технологию после более чем десятилетней разработки.

24 мая 2017 года Samsung выпустила пресс-релиз своей обновленной дорожной карты. Из-за задержек с введением EUVL Samsung представит новый процесс, называемый 8-нм LPP, чтобы преодолеть разрыв между 10-нм и 7-нм. Процесс будет производиться без использования EUVL и будет иметь немного уменьшенный размер транзистора.

Из-за задержек с введением EUVL Samsung представит новый процесс, называемый 8-нм LPP, чтобы преодолеть разрыв между 10-нм и 7-нм. Процесс будет производиться без использования EUVL и будет иметь немного уменьшенный размер транзистора.

7LPE[править]

7LPP[править]

GlobalFoundries[править]

- Примечание.

30 мая 2017 года старший вице-президент GlobalFoundries и глава бизнес-подразделения CMOS Грегг Бартлетт объявил об обновленной дорожной карте. Вместо EUV компания будет использовать множественный паттерн 193i для своего 7-нм узла. Компания планирует выпустить первую ленту во второй половине 2018 года, а массовое производство начнется в 2019 году.. Бартлетт отметил, что GF переключится на EUVL, когда будет готово.

7-нм техпроцесс включает SAQP для FEOL и двойную структуру для BEOL. GlobalFoundries заявляет об улучшении плотности в 2,8 раза по сравнению с их 14-нм техпроцессом и повышении производительности на 40% или снижении энергопотребления на 55%. Будут разработаны две версии процесса: версия с низким энергопотреблением для мобильных приложений. И высокопроизводительная версия для настольных и серверных чипов.

Будут разработаны две версии процесса: версия с низким энергопотреблением для мобильных приложений. И высокопроизводительная версия для настольных и серверных чипов.

7LP[править]

7HPC[править]

Микропроцессоры 7 нм[править]

- PEZY

- ПЕЗИ-SC3

- МедиаТек

- Гелио М70

- РАЗМЕР 1000

- Размер 800U

- Размерность 1000+

- Размер 800

- яблоко

- А12

- А12Х

- А13

- HiSilicon (Хуавэй)

- 990 4G/5G

- 980

- 810

- Львиный зев (Qualcomm)

- Львиный зев 765G

- 855

- 865

- 870

- Львиный зев 865+

- Exynos (Самсунг)

- 990

- 9825

Этот список неполный; Вы можете помочь, расширив это.

Микроархитектуры 7 нм[править]

- AMD

- Вега 20

- Нави

- Дзен 2

- Дзен 3

- Ампер

- Ртуть

- Эсперанто

- ET-миньон

- ET-Maxion

- Интел

- Гранитные пороги

- Метеоритное озеро

-

Knights Peak

См.

Также [Edit]

Также [Edit]

- История технологии процесса Intel

Bibliography [edit]

- IBM, Conference Confereneries, Conference Confereneries, Conferenge Confereneries, ConferenceE, ConferenceE, 201613

- IBM, Conference Confereneries. ).

- Samsung, 2016 г. 62-я Международная встреча IEEE по электронным устройствам (IEDM).

- TSMC, Международная конференция IEEE по твердотельным схемам (ISSCC), 2017 г.

- Qualcomm, TSMC, Симпозиум по технологиям и схемам СБИС, 2019 г. (VLSI 2019).

Процесс литографии 7 нм — WikiChip

- 1 нм

- 2 нм

- 3 нм

- 5 нм

- 7 нм

- 10 нм

- 14 нм

- 16 нм

- 20 нм

- 22 нм

- 28 нм

- 32 нм

- 40 нм

- 45 нм

- 55 нм

- 65 нм

- 80 нм

- 90 нм

- 110 нм

- 130 нм

- 150 нм

- 180 нм

- 220 нм

- 240 нм

- 250 нм

- 280 нм

- 350 нм

- 500 нм

- 600 нм

- 650 нм

- 700 нм

- 750 нм

- 800 нм

- 1 мкм

- 1,2 мкм

- 1,3 мкм

- 1,5 мкм

- 2 мкм

- 2,5 мкм

- 3 мкм

- 3,5 мкм

- 5 мкм

- 6 мкм

- 7 мкм

- 8 мкм

- 10 мкм

- 16 мкм

- 20 мкм

- 50 мкм

v · d · e

Массовое производство интегральных схем, изготовленных с использованием 7-нм техпроцесса, началось в 2018 году.

К 2020/21 году передовые литейные производства будут поэтапно отказываться от этого техпроцесса, где он будет заменен 5-нм узлом.

К 2020/21 году передовые литейные производства будут поэтапно отказываться от этого техпроцесса, где он будет заменен 5-нм узлом.Термин «7 нм» — это просто коммерческое название поколения определенного размера и его технологии, а не представляет собой какую-либо геометрию транзистора.

Содержание

- 1 Обзор

- 1.1 Плотность

- 2 Промышленность

- 2.1 Интел

- 2.1.1 Интел 7

- 2.1.1.1 Intel 7 Ультра

- 2.1.1 Интел 7

- 2.2 ТСМС

- 2.2.1 N7

- 2.2.1.1 Стандартные ячейки

- 2.2.2 N7P

- 2.2.3 N7+

- 2.2.1 N7

- 2.3 Самсунг

- 2.3.1 7ЛПЭ

- 2.3.2 7ЛПП

- 2.4 GlobalFoundries

- 2.4.1 7LP

- 2.4.2 7HPC

- 2.1 Интел

- 3 микропроцессора 7 нм

- 4 микроархитектуры 7 нм

- 5 См. также

- 6 Библиография

Обзор[править]

Впервые представленный крупными литейными заводами в период с 2018 по 2019 год, 7-нанометровый технологический процесс характеризуется использованием транзисторов FinFET с шагом ребер в 30 нанометров и плотным металлическим шагом в верхней части.

30 или менее 50 нанометров. Из-за небольших размеров элементов для некоторых слоев пришлось использовать четырехъядерный паттерн. Этот процесс был введен как раз тогда, когда литография EUV была готова к массовому производству, поэтому некоторые литейные заводы использовали EUV, а другие нет.

30 или менее 50 нанометров. Из-за небольших размеров элементов для некоторых слоев пришлось использовать четырехъядерный паттерн. Этот процесс был введен как раз тогда, когда литография EUV была готова к массовому производству, поэтому некоторые литейные заводы использовали EUV, а другие нет.Плотность[править]

С точки зрения исходной плотности на уровне ячеек, 7-нанометровый узел имеет плотность кремния от 90 до 102 миллионов транзисторов на квадратный миллиметр, согласно собственному анализу WikiChip.

Промышленность[править]

Только три компании в настоящее время планируют или разрабатывают 7-нанометровый узел: Intel, TSMC и Samsung.

Intel TSMC Samsung GlobalFoundries Process P1276 (CPU), P1277 (SoC) N7, N7P, N7+ 7LPE, 7LPP 7LP, 7HPProduction 2021 April 2018 April 2019 Cancelled Litho Lithography EUV DUV ⇒ EUV EUV DUV ⇒ EUV Immersion

ExposureSADP ⇒ SE (EUV)

DP (193i)SE (EUV)

DP (193i)SADP ⇒ SE (EUV)

DP (193i)Wafer Type Bulk Size 300 mm xTor Type FinFET Voltage Value 10 nm Δ Value 10 nm Δ Value 10 nm Δ Value 14 nm Δ Fin Pitch 30 nm 0.  83x

83x27 nm 0.64x 30 nm 0.625x Width 6 nm 1.00x Height 52 nm 1.24x Gate Length (L g ) 8/10 nm Contacted Gate Pitch (CPP) 64 nm (HP )

57 нм (HD)0,82x 60 нм (HP)

54 нм (HD)0,79x 56 нм 0,72x 1919. Мини. 40 нм 0,95x 36 нм 0,75x 40 нм 0,625x SRAM High-Perf (HP) 9 9 9000 0,030 М.  0.44x

0.44xHigh-Density (HD) 0.027 µm² 0.64x 0.026 µm² 0.65x 0.0269 µm² 0.42x Low-Voltage (LV) Intel[править]

Intel 7[править]

Intel 7 Ultra[править]

Новая кривая Intel V-F 7 для процесса Enhance.

Intel представила расширенную версию процесса Intel 7 в конце 2022 года с выпуском процессоров Core 13-го поколения на базе микроархитектуры Raptor Lake. Новый процесс, получивший внутреннее прозвище «Intel 7 Ultra» , представляет собой полное обновление PDK по сравнению с тем, который используется Alder Lake, их архитектурой SuperFin Transistor 3-го поколения. Intel заявляет, что этот процесс позволяет получить транзисторы со значительно лучшей мобильностью каналов. Компания заявляет, что на самом верхнем конце кривой V-F пиковая частота теперь почти на 1 ГГц выше.

Сама кривая была улучшена, сдвинув частоты предыдущего поколения примерно на 200 МГц при напряжении ISO или, альтернативно, снизив напряжение более чем на 50 мВ при частоте ISO.

Сама кривая была улучшена, сдвинув частоты предыдущего поколения примерно на 200 МГц при напряжении ISO или, альтернативно, снизив напряжение более чем на 50 мВ при частоте ISO.TSMC[править]

TSMC начала массовое производство своего 7-нанометрового узла N7 в апреле 2018 года. Хотя TSMC выпустила 10-нанометровый узел годом ранее, компания считала его 10-нм узлом недолговечным и предназначалась для обучения узлу на пути к 7. В начале 2019 года TSMC представила вторую версию технологического процесса. его процесс N7 называется N7P , что обеспечивает дополнительные улучшения производительности. С появлением высокопроизводительных машин EUV, готовых к массовому производству, TSMC представила третий вариант под названием 9.0122 N7+ , использующий EUV.

N7[править]

Обзор N7

Оригинальный TSMC 7-нанометровый процесс N7 был представлен в апреле 2018 года. По сравнению с собственной 16-нанометровой технологией, TSMC утверждает, что ее 7-нанометровый узел обеспечивает повышение скорости примерно на 35-40%.

или на 65% ниже мощность. Говорят, что по сравнению с 10-нм узлом с половинным узлом N7 обеспечивает повышение скорости на ~ 20% или снижение энергопотребления на ~ 40%. Говорят, что с точки зрения плотности N7 обеспечивает улучшение в 1,6 и 3,3 раза по сравнению с N10 и N16 соответственно. N7 в значительной степени основан на всех предыдущих процессах FinFET, которые компания использовала ранее. С этой целью это FinFET четвертого поколения, HKMG пятого поколения, последний затвор, оксидный процесс с двумя затворами.

или на 65% ниже мощность. Говорят, что по сравнению с 10-нм узлом с половинным узлом N7 обеспечивает повышение скорости на ~ 20% или снижение энергопотребления на ~ 40%. Говорят, что с точки зрения плотности N7 обеспечивает улучшение в 1,6 и 3,3 раза по сравнению с N10 и N16 соответственно. N7 в значительной степени основан на всех предыдущих процессах FinFET, которые компания использовала ранее. С этой целью это FinFET четвертого поколения, HKMG пятого поколения, последний затвор, оксидный процесс с двумя затворами.N7 PPA против N16 Скорость при изо-мощности Мощность при скорости ISO Плотность ~30% ~55% ~3,3x N7 PPA против N10 Скорость при изо-мощности Мощность при скорости ISO Плотность ~20% ~40% ~1,6x Вт эфф для TSMC 16, 10 и 7 нм.

Для N7 TSMC продолжала использовать иммерсионную литографию ArF с длиной волны 193 нм в глубоком ультрафиолете (DUV). Ограничения i193 диктовали некоторые правила проектирования процесса. Для транзистора шаг затвора был дополнительно уменьшен до 57 нм, однако шаг межсоединений был остановлен на отметке 40 нм, чтобы сохранить структуру в точке SADP. Правила проектирования были тщательно разработаны, чтобы оставаться в рамках двойного шаблона. Единичный паттерн был немного продвинут до точки 76 нанометров. Правила проектирования для N7 показаны ниже.

Правила проектирования TSMC N7 Слой Шаг (нм) Моделирование Примечания Плавник 30 СКП Поли 57 САДП М0 40 САДП Мкс М1 40 САДП 1x М2 40 САДП 1x М3 40 САДП 1x М4 40 САДП 1x М5 76 Одноместный 1,9x М6 76 Одноместный 1,9x М7 76 Одноместный 1,9x М8 76 Одноместный 1,9x М9 76 Одноместный 1,9x М10 124 Одноместный 3,1x М11, М12 720 Одноместный 18x Стоит отметить, что агрессивное масштабирование шага ребер привело к довольно плотным битовым ячейкам SRAM.

Размер битовой ячейки SRAM высокой плотности N7 составляет 0,027 мкм².

Размер битовой ячейки SRAM высокой плотности N7 составляет 0,027 мкм².Распространение элементов SoC Apple A12 (MSS Corp). Видны кобальтовые контакты.

Профиль транзистора также был улучшен. Как и в 10-нанометровом техпроцессе Intel, TSMC представила кобальтовое наполнение траншейных контактов, заменив вольфрамовые контакты. Это приводит к снижению сопротивления в этой области на 50%. Некоторые преимущества масштабирования площади и затрат были достигнуты за счет масштабирования шага / высоты ребра. Продолжая масштабировать ширину ребра, вы получаете более узкий канал, в то время как увеличение высоты для поддержания хорошей эффективной ширины делается для того, чтобы улучшить характеристики короткого канала и подпороговый наклон (т. е. улучшить Ieff / Ceff), но это также ухудшает общие паразитные характеристики. Имейте в виду, что в целом задержка устройства CV/I все же лучше, потому что собственная емкость, такая как Cgate и Cov, по-прежнему зависит от Ieff.

Еще один способ визуализировать эффект масштабирования ширины и высоты — использовать эффективную ширину. На графике, показанном слева, мы нанесли эффективную ширину от 16 нанометров TSMC до текущего 7-нанометрового узла. По сравнению с N16, N7 имеет более чем в два раза большую эффективную ширину канала.

Для этого процесса были разработаны различные многовольтные устройства с диапазоном Vt около 200 мВ.

Стандартные ячейки Эти клетки имеют высоту 240 нм и 300 нм соответственно. До выхода на полную производственную мощность у TSMC изначально было 9Вариант T HP, который опирался на 57-нм CPP. Эта библиотека в конечном итоге устарела в пользу 64-нм библиотеки CPP 7.5T, которая сейчас используется в массовом производстве различными компаниями. Обратите внимание, что модели 7,5T и 9T схожи по мощности и производительности. Некоторые ранние проекты, которые начинались с библиотеки 9T, продолжали использовать ее, несмотря ни на что.

Тип Высокая плотность Высокая производительность Название h340 HD h400 HP H460 HP FIN PINKE 30 нм Металл 40 нм (наименьшая высота, используемая с DP)

76 нм (самый маленький шаг с SP)9 76 нм (самый маленький шах 64 нм 57 нм Высота 240 нм

8-фин X 30 нм300 нм

10-финал X 30 нм360 нм

12-FIN x 30 NM360 Нм

12-FIN X 30 NM99999.  360 Нм

360 Нм

12-FIN x 30 0009360 нм

12-фина6 Т 7,5 т 9 т Qualcomm Snapdragon 855Ieff разница между ячейками HD и HP. (VLSI 2019)

Компания Qualcomm сообщила, что на ее собственной SoC (Snapdragon 855) высокопроизводительные элементы обеспечивают примерно на 10-13% более высокий эффективный управляющий ток (Ieff), хотя и за счет того, что транзисторы немного менее герметичны. Основываясь на собственном анализе WikiChip, плотные ячейки имеют около 91,2 МТр/мм², в то время как менее плотные высокопроизводительные ячейки рассчитываются примерно на уровне 65 МТр/мм².

N7P[править]

Улучшения N7P (2-го поколения) по сравнению с N7 (1-го поколения). (VLSI 2019)

В 2019 году TSMC представила процесс N7 2-го поколения под названием N7 Performance-Enhanced ( N7P ). N7P — это оптимизированная версия процесса TSMC N7.

с этой целью он остается процессом, основанным на DUV, с соблюдением тех же правил проектирования и полностью IP-совместим с N7. N7P вводит оптимизации FEOL и MOL, которые, как говорят, приводят либо к повышению производительности на 7% при мощности изо, либо к снижению энергопотребления до 10% при скорости изо.

с этой целью он остается процессом, основанным на DUV, с соблюдением тех же правил проектирования и полностью IP-совместим с N7. N7P вводит оптимизации FEOL и MOL, которые, как говорят, приводят либо к повышению производительности на 7% при мощности изо, либо к снижению энергопотребления до 10% при скорости изо.N7 PPA против N7P Скорость при изо-мощности Мощность @ ISO-скорость ~7% ~10% Для своего процесса второго поколения TSMC внесла некоторые дополнительные оптимизации, включая оптимизацию профиля ребер, эпиоптимизацию, оптимизацию сопротивления MOL, уменьшение емкости FEOL и оптимизацию металлических затворов. Кроме того, при той же утечке на высоких частотах 7-нм техпроцесс второго поколения улучшил Vmin на 50 мВ.

N7+[править]

Узел N7+ — первая технология TSMC, использующая литографию EUV. Он не связан ни с процессами N7, ни с N7P и не совместим с IP ни с одним из них, что требует повторной реализации (новой физической схемы и проверки).

N7+ поступил в массовое производство во втором квартале 2019 года и использует EUV для четырех критических слоев. Говорят, что по сравнению с процессом TSMC N7, N7+ обеспечивает повышение плотности примерно в 1,2 раза. Также сообщается, что N7+ обеспечивает на 10% более высокую производительность при изо-мощности или, в качестве альтернативы, до 15% более низкое энергопотребление при изо-производительности. На бумаге N7+ кажется немного лучше, чем N7P, хотя это достигается за счет повторной реализации дизайна.

N7+ поступил в массовое производство во втором квартале 2019 года и использует EUV для четырех критических слоев. Говорят, что по сравнению с процессом TSMC N7, N7+ обеспечивает повышение плотности примерно в 1,2 раза. Также сообщается, что N7+ обеспечивает на 10% более высокую производительность при изо-мощности или, в качестве альтернативы, до 15% более низкое энергопотребление при изо-производительности. На бумаге N7+ кажется немного лучше, чем N7P, хотя это достигается за счет повторной реализации дизайна.N7 PPA против N7+ Скорость при изо-мощности Мощность при скорости ISO Плотность ~10% ~15% 1,2x Samsung[править]

Samsung будет использовать EUVL для своего 7-нм узла и, таким образом, станет первой, кто представит эту новую технологию после более чем десятилетней разработки.

24 мая 2017 года Samsung выпустила пресс-релиз своей обновленной дорожной карты. Из-за задержек с введением EUVL Samsung представит новый процесс, называемый 8-нм LPP, чтобы преодолеть разрыв между 10-нм и 7-нм. Процесс будет производиться без использования EUVL и будет иметь немного уменьшенный размер транзистора.

Из-за задержек с введением EUVL Samsung представит новый процесс, называемый 8-нм LPP, чтобы преодолеть разрыв между 10-нм и 7-нм. Процесс будет производиться без использования EUVL и будет иметь немного уменьшенный размер транзистора.7LPE[править]

7LPP[править]

GlobalFoundries[править]

- Примечание.

30 мая 2017 года старший вице-президент GlobalFoundries и глава бизнес-подразделения CMOS Грегг Бартлетт объявил об обновленной дорожной карте. Вместо EUV компания будет использовать множественный паттерн 193i для своего 7-нм узла. Компания планирует выпустить первую ленту во второй половине 2018 года, а массовое производство начнется в 2019 году.. Бартлетт отметил, что GF переключится на EUVL, когда будет готово.

7-нм техпроцесс включает SAQP для FEOL и двойную структуру для BEOL. GlobalFoundries заявляет об улучшении плотности в 2,8 раза по сравнению с их 14-нм техпроцессом и повышении производительности на 40% или снижении энергопотребления на 55%.

Будут разработаны две версии процесса: версия с низким энергопотреблением для мобильных приложений. И высокопроизводительная версия для настольных и серверных чипов.

Будут разработаны две версии процесса: версия с низким энергопотреблением для мобильных приложений. И высокопроизводительная версия для настольных и серверных чипов.7LP[править]

7HPC[править]

Микропроцессоры 7 нм[править]

- PEZY

- ПЕЗИ-SC3

- МедиаТек

- Гелио М70

- РАЗМЕР 1000

- Размер 800U

- Размерность 1000+

- Размер 800

- яблоко

- А12

- А12Х

- А13

- HiSilicon (Хуавэй)

- 990 4G/5G

- 980

- 810

- Львиный зев (Qualcomm)

- Львиный зев 765G

- 855

- 865

- 870

- Львиный зев 865+

- Exynos (Самсунг)

- 990

- 9825

Этот список неполный; Вы можете помочь, расширив это.

Микроархитектуры 7 нм[править]

- AMD

- Вега 20

- Нави

- Дзен 2

- Дзен 3

- Ампер

- Ртуть

- Эсперанто

- ET-миньон

- ET-Maxion

- Интел

- Гранитные пороги

- Метеоритное озеро

-

Knights Peak

См.

также

также К 2020/21 году передовые литейные производства будут поэтапно отказываться от этого техпроцесса, где он будет заменен 5-нм узлом.

К 2020/21 году передовые литейные производства будут поэтапно отказываться от этого техпроцесса, где он будет заменен 5-нм узлом. 30 или менее 50 нанометров. Из-за небольших размеров элементов для некоторых слоев пришлось использовать четырехъядерный паттерн. Этот процесс был введен как раз тогда, когда литография EUV была готова к массовому производству, поэтому некоторые литейные заводы использовали EUV, а другие нет.

30 или менее 50 нанометров. Из-за небольших размеров элементов для некоторых слоев пришлось использовать четырехъядерный паттерн. Этот процесс был введен как раз тогда, когда литография EUV была готова к массовому производству, поэтому некоторые литейные заводы использовали EUV, а другие нет. 83x

83x 0.44x

0.44x Сама кривая была улучшена, сдвинув частоты предыдущего поколения примерно на 200 МГц при напряжении ISO или, альтернативно, снизив напряжение более чем на 50 мВ при частоте ISO.

Сама кривая была улучшена, сдвинув частоты предыдущего поколения примерно на 200 МГц при напряжении ISO или, альтернативно, снизив напряжение более чем на 50 мВ при частоте ISO. или на 65% ниже мощность. Говорят, что по сравнению с 10-нм узлом с половинным узлом N7 обеспечивает повышение скорости на ~ 20% или снижение энергопотребления на ~ 40%. Говорят, что с точки зрения плотности N7 обеспечивает улучшение в 1,6 и 3,3 раза по сравнению с N10 и N16 соответственно. N7 в значительной степени основан на всех предыдущих процессах FinFET, которые компания использовала ранее. С этой целью это FinFET четвертого поколения, HKMG пятого поколения, последний затвор, оксидный процесс с двумя затворами.

или на 65% ниже мощность. Говорят, что по сравнению с 10-нм узлом с половинным узлом N7 обеспечивает повышение скорости на ~ 20% или снижение энергопотребления на ~ 40%. Говорят, что с точки зрения плотности N7 обеспечивает улучшение в 1,6 и 3,3 раза по сравнению с N10 и N16 соответственно. N7 в значительной степени основан на всех предыдущих процессах FinFET, которые компания использовала ранее. С этой целью это FinFET четвертого поколения, HKMG пятого поколения, последний затвор, оксидный процесс с двумя затворами.

Размер битовой ячейки SRAM высокой плотности N7 составляет 0,027 мкм².

Размер битовой ячейки SRAM высокой плотности N7 составляет 0,027 мкм².

360 Нм

360 Нм  с этой целью он остается процессом, основанным на DUV, с соблюдением тех же правил проектирования и полностью IP-совместим с N7. N7P вводит оптимизации FEOL и MOL, которые, как говорят, приводят либо к повышению производительности на 7% при мощности изо, либо к снижению энергопотребления до 10% при скорости изо.

с этой целью он остается процессом, основанным на DUV, с соблюдением тех же правил проектирования и полностью IP-совместим с N7. N7P вводит оптимизации FEOL и MOL, которые, как говорят, приводят либо к повышению производительности на 7% при мощности изо, либо к снижению энергопотребления до 10% при скорости изо. N7+ поступил в массовое производство во втором квартале 2019 года и использует EUV для четырех критических слоев. Говорят, что по сравнению с процессом TSMC N7, N7+ обеспечивает повышение плотности примерно в 1,2 раза. Также сообщается, что N7+ обеспечивает на 10% более высокую производительность при изо-мощности или, в качестве альтернативы, до 15% более низкое энергопотребление при изо-производительности. На бумаге N7+ кажется немного лучше, чем N7P, хотя это достигается за счет повторной реализации дизайна.

N7+ поступил в массовое производство во втором квартале 2019 года и использует EUV для четырех критических слоев. Говорят, что по сравнению с процессом TSMC N7, N7+ обеспечивает повышение плотности примерно в 1,2 раза. Также сообщается, что N7+ обеспечивает на 10% более высокую производительность при изо-мощности или, в качестве альтернативы, до 15% более низкое энергопотребление при изо-производительности. На бумаге N7+ кажется немного лучше, чем N7P, хотя это достигается за счет повторной реализации дизайна. Будут разработаны две версии процесса: версия с низким энергопотреблением для мобильных приложений. И высокопроизводительная версия для настольных и серверных чипов.

Будут разработаны две версии процесса: версия с низким энергопотреблением для мобильных приложений. И высокопроизводительная версия для настольных и серверных чипов.